Se puede entender que, tras décadas predicando la buena nueva, a Intel le cueste reconocer que aquel viejo principio de voluntarismo industrial que el mundo conoce como ´ley` de Moore ha alcanzado un punto de insostenibilidad. Lo que sí hará Intel será desmantelar una de sus consecuencias, la cadencia del proceso de fabricación. La compañía ha comunicado al regulador bursátil de Estados Unidos un hecho relevante: «esperamos extender el tiempo de vigencia de nuestra tecnología de 14 nanometros y, en consecuencia, pospondremos la puesta en marcha de la siguiente generación de 10 nanometros [para, en cambio] optimizar los procesos de producción sin afectar el ritmo anual de nuestros productos».

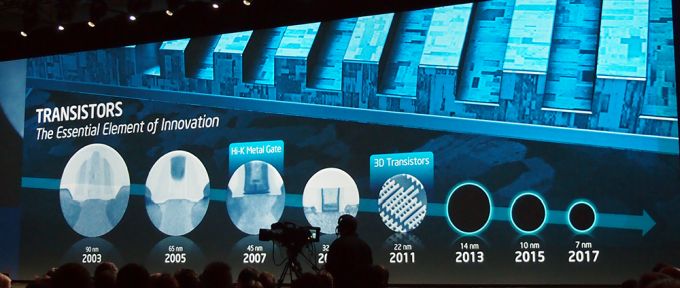

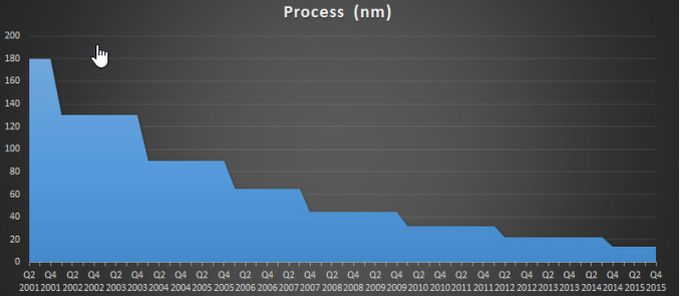

La frase contiene muchos elementos que este post tratará de desplegar con la paciencia del lector. Ahí va el primero: implica que el avance de los procesadores y memorias que fabrica Intel no podrá apoyarse tanto en la miniaturización – clave del postulado de Moore – sino más bien en el rediseño de su circuitería y arquitectura interna. Cada dos años desde hace medio siglo, con calculada regularidad, se ha reducido a la mitad la separación entre los transistores: 2014 fue el año de los 14 nanómetros (16, en el caso de otros fabricantes) y para 2016 estaba previsto fabricar a escala industrial chips de 10 nanómetros.

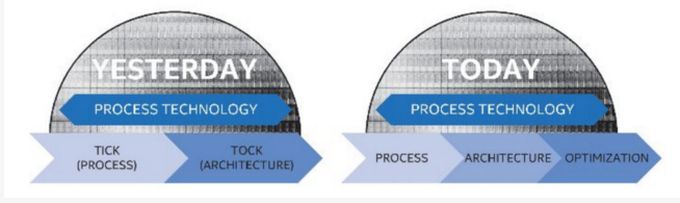

Desde hace una década, la rutina industrial de Intel ha descansado sobre la metodología tick-tock, adoptada por primera vez con la familia Core: según este esquema, la fase tick corresponde a la migración de un diseño existente a un nuevo proceso de fabricación, gradualmente más denso; en la fase tock, ese nuevo proceso da origen a una microarquitectura; cada una de las fases se encarna en un producto, con lo que se asegura a la vez la continuidad y la renovación de la oferta. Normalmente, debería haber un desfase de 12 a 18 meses entre tick y tock. Esta cadencia es la que Intel abandona, por razones que se verán: en lugar de reducir el tamaño de sus chips cada dos años, lo hará cada tres años.

Tanto o más que la ´ley` de Moore, la cadencia tick-tock es un acto de voluntad, cuyos condicionantes directos son el estado de la técnica, el monto de la inversión y la situación del mercado. Ya el año pasado, Intel admitió que su futuro procesador Cannonlake de 10 nm (el siguiente tick) no estaría listo hasta 2017, por lo que extendería la vida del Skylake de 14 nm (el tock precedente). Para cumplir el compromiso de sacar al mercado un procesador nuevo al año [sin lo cual el mercado del PC se deprimiría aún más a falta de novedad] anunció el adelanto de Kaby Lake, ni tick ni tock. El truco consiste en cambiar la terminología: ahora se habla de una secuencia de tres partes: proceso / arquitectura / optimización.

Durante los primeros 30 años de esta industria, entre 1965 y 1995 aproximadamente, las prestaciones de los circuitos integrados mejoraban sustancialmente gracias a la reducción de tamaño de los transistores, componente primario de todo chip; en la misma superficie cabían más transistores, lo que aumentaba su frecuencia de funcionamiento, se podían hacer más operaciones por segundo, y gracias a ello se pudieron diseñar sistemas cada vez más potentes y complejos.

Fueron los años dorados de la revolución digital. Los beneficios que suponía la miniaturización de los transistores y, consecuentemente, el escalado geométrico de los chips, justificaban las elevadas inversiones necesarias para fabricarlos más densos, con aproximadamente el doble de transistores por unidad de superficie, cada dos años. Este ritmo frenético, con sus consecuencias, es lo que vislumbró Gordon Moore en 1965 , aunque lo recalculó a la baja diez años después. El texto seminal de Moore nunca pretendió ser una ley de la física, sino una meta industrial cuyo cumplimiento requeriría un caudal de inversión y un crecimiento acorde de la demanda.

Hacia 1995 ya estaba claro que no se podía seguir reduciendo el tamaño de los transistores sólo con escalado geométrico. Un análisis de la familia Pentium – producto estrella de la época – reveló que la mitad de la energía consumida se perdía en las interconexiones, generando un calor imposible de evacuar. Los procesadores consumían más de 100 vatios, lo que hacía inviable seguir aumentando la frecuencia de funcionamiento de los transistores al mismo ritmo porque se fundirían, literalmente, todos los circuitos.

Durante los veinte años siguientes, hasta hace muy poco, se ha procedido a rediseñar completamente el proceso de fabricación y la estructura de los transistores, para aminorar la pérdida de energía. El nuevo paradigma de fabricación se conoce como escalado equivalente, y es lo que ha permitido mantener, a trancas y barrancas, la ´ley` de Moore.

Sin superar el límite de consumo de energía de un vatio por milímetro cuadrado, se ha conseguido seguir aumentando el número de transistores en cada chip. Los procesadores han pasado de 100 transistores en 1965 a un millón en 1990 y a 1.000 millones a principios de esta década. Los chips actuales ya superan los 5.000 millones de transistores, y el tamaño de las pistas de diseño ha pasado de las cinco micras (5.000 nanometros) en 1972 a los 14 nanometros en el presente.

Lo que no ha podido aumentarse es la frecuencia de funcionamiento, cuyo máximo es de 3,5 gigahercios. Ha aumentado el número de núcleos en un chip, y ahora es usual que tengan hasta una docena. Pero las prestaciones brutas no han aumentado en lo esencial. El beneficio de la mayor integración ha consistido en incluir más funciones dentro del chip, hasta llegar a un sistema completo (SoC) como ocurre en los smartphones: un solo chip lo hace prácticamente todo, desde el procesamiento de datos hasta las comunicaciones y la gestión de gráficos.

Intel ha sido la compañía de semiconductores que más se ha beneficiado de las ventajas inherentes al escalado, porque siempre se ha dedicado a la fabricación de procesadores y memorias, que tienen una estructura interna repetitiva. La necesidad de hacer procesadores más potentes y memorias más densas impulsaba el desarrollo tecnológico y justificaba los recursos financieros destinados a ese fin. La ´ley` de Moore resultó ser la cobertura perfecta. En las actuales condiciones, resulta difícil justificar una carrera que no aporta más rentabilidad con cada proceso. Esta es, por encima de todo, una cuestión económica; de ahí que Intel decidiera comunicarla a sus accionistas por mediación de un formulario 10K presentado a la SEC (comisión de valores estadounidense).

Ya hace dos generaciones de proceso, a la altura de los 32 nm, se vio que los nuevos microprocesadores introducidos en el mercado por Intel no eran muy superiores a los anteriores de 45 nm. Al tener más superficie libre, se podía poner más memoria caché o unos gráficos superiores, y la distancia que debían recorrer los electrones era menor, pero las limitaciones de frecuencia y de consumo de energía hacían que los PC portátiles resultantes no fueran mucho más potentes que la generación precedente. La fidelidad a la arquitectura x86 para hacerlos compatibles con todo lo existente, dejaba poco margen de mejora en la generación de 22 nm, y mucho menos en la de 14 nm, que es la actual.

Intel confía en que la obligada desaceleración en la implantación de nuevas técnicas de proceso frenará también a sus competidores, y le permitirá seguir liderando la industria de semiconductores. La realidad es que los rivales han ido acortando en los últimos años la introducción de esas nuevas técnicas. Samsung adoptó en 2015, pocos meses después de que lo hiciera Intel, los 14 nanómetros, y el pasado enero optimizó la tecnología para que sus chips consumieran menos energía.

También TSMC y GlobalFoundries han acortado los plazos. Los cuatro contendientes están poniendo a punto la tecnología de 10 nanómetros y ya investigan la de 7 nm. A lo largo de 2017 o 2018, las cuatro compañías podrían haber empezado a fabricar chips de 10 nm en volumen con pocos meses de diferencia, para llegar en 2020 a los de 7 nm. Más allá, los 5 nm son factibles pero no antes de 2023, probablemente en cantidades industriales a partir de 2025.

Hay aquí hay otro elemento a considerar: la competencia. Samsung y TSMC tienen las mismas dificultades tecnológicas y económicas que Intel para reducir el tamaño de los transistores. Pero cuentan con una cartera de productos diversificada y, además, fabrican para empresas que diseñan sus propios chips (fabless). Integran sistemas completos, que son muy rentables y mejoran las prestaciones de los dispositivos: los ejemplos típicos son los SoC que Samsung y TSMC producen para Qualcomm, MediaTek y Apple (o la propia Samsung).

Más que la evolución de los procesos de fabricación, el problema crucial de la industria de semiconductores es su rentabilidad. Porque la inversión necesaria en maquinaria para poner a punto cada generación tecnológica es muy alta, unos 5.000 millones de dólares, y las mejoras que se obtienen son (relativamente) marginales.

Los dispositivos digitales de los próximos años, sobre todo los del Internet de las Cosas, requerirán chips no necesariamente diminutos ni con 5.000 millones de transistores de 10 nm, sino piezas de silicio simples, frugales y baratas, que se podrían fabricar con tecnologías ya amortizadas e innovando en los diseños. Intel lo sabe, y lleva años diversificando su cartera, pero los nuevos segmentos de mercado no crecen (todavía) al ritmo que sería preciso para compensar la decadencia de otros. Para colmo, se quedó descolgada del mercado de los smartphones y ese error lo está pagando caro.

Ha sido una desdichada coincidencia que la noticia se publicara en los días previos a la muerte de Andy Grove, legendario ex CEO de Intel y considerado como el auténtico propagandista de la hipótesis de Gordon Moor transformada en ´ley` de Moore. Brian Krzanich, el actual CEO, ya habia sugerido que habría algún retraso en la cadencia tick-tock, y tenía que hacerlo oficial antes de dos circunstancias inminentes: en abril, Krzanich presentará los resultados del primer trimestre, que probablemente determinarán un bajón en las inversiones de capital, y también protagonizará en Shenzhen la ediciòn china del IDF (Intel Development Forum) en el que va a mostrar sus cartas en materia de productos futuros.

Los obituarios dedicados en los últimos días a Andy Grove destacan una de sus muchas frases célebres: «sólo los paranoicos sobreviven» [título, por lo demás, de un libro autobiográfico]. Pues bien, para asegurar el futuro de Intel, parece llegado el momento de darse un respiro en esa profecía autocumplida que es la ´ley` de Moore. Sin renunciar al mensaje, pasar de una cadencia endiablada de dos años a otra más serena (y económica) de tres años está más que justificado. La advertencia de Grove, dicha en otras circunstancias, puede reinterpretarse así: ser cuerdos y razonables en un mundo de paranoicos puede ser una fórmula de supervivencia para los tiempos que vienen.

[informe de Lluís Alonso]